دانشکده مهندسی کامپیوتر خبرداد:

در ادامه سلسله وبینارهای تخصصی دانشکده مهندسی کامپیوتر، وبیناری حول موضوع محوری بهبود قابلیت اطمینان در ساختار حافظه ها با سخنرانی خانم دکتر مرجان اسدی نیا برگزار می شود. از عموم علاقمندان دعوت می شود در این جلسه شرکت نمایند.

موضوع وبینار:

Improving Reliability and Durability of Phase Change Main Memories

زمان برگزاری: ۱۴ بهمن ماه ۱۳۹۹، ساعت ۱۲:۰۰

سخنران وبینار:

Dr Marjan Asadinia

Postdoctoral Fellow at University of Arkansas

لینک ورود به جلسه:

https://vc.sru.ac.ir/r2piagg0nkbq/

خلاصه ای از محتوای وبینار:

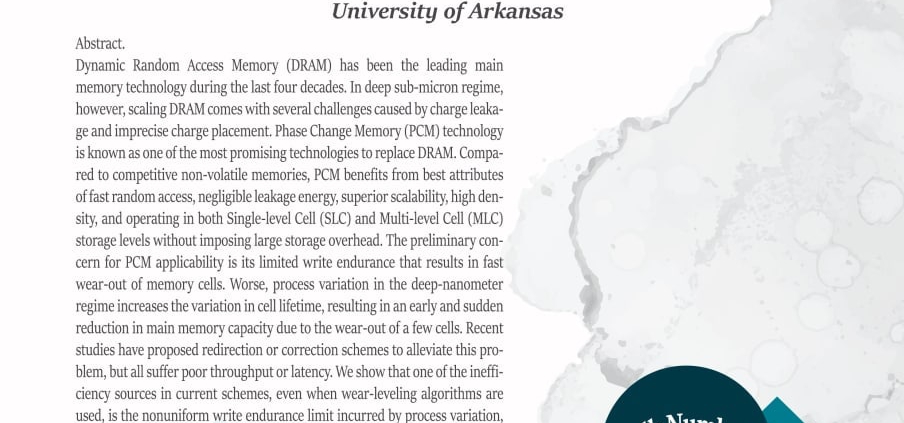

Dynamic Random Access Memory (DRAM) has been the leading main memory technology during the last four decades. In deep sub-micron regime, however, scaling DRAM comes with several challenges caused by charge leakage and imprecise charge placement. Phase Change Memory (PCM) technology is known as one of the most promising technologies to replace DRAM. Compared to competitive non-volatile memories, PCM benefits from best attributes of fast random access, negligible leakage energy, superior scalability, high density, and operating in both Single-level Cell (SLC) and Multi-level Cell (MLC) storage levels without imposing large storage overhead. The preliminary concern for PCM applicability is its limited write endurance that results in fast wear-out of memory cells. Worse, process variation in the deep-nanometer regime increases the variation in cell lifetime, resulting in an early and sudden reduction in main memory capacity due to the wear-out of a few cells. Recent studies have proposed redirection or correction schemes to alleviate this problem, but all suffer poor throughput or latency. We show that one of the inefficiency sources in current schemes, even when wear-leveling algorithms are used, is the nonuniform write endurance limit incurred by process variation, that is, when some memory pages have reached their endurance limit, other pages may be far from their limit. In this line, we present a technique that aims to displace a faulty page to a healthy page. This technique, when applied at page level, can improve PCM time-to-failure by 20% on average for different multithreaded and multiprogrammed workloads while also improving IPC by 14% on average compared to previous page-level techniques.